# Muon-Induced SEU Analysis and Simulation for Different Cell Types in 12-nm FinFET SRAMs, and 28-nm Planar SRAMs and Register Files

Yuibi Gomi<sup>®</sup>, Kazusa Takami, Rurie Mizuno<sup>®</sup>, Megumi Niikura<sup>®</sup>, Ryuichi Yasuda<sup>®</sup>, Yifan Deng<sup>®</sup>, Shoichiro Kawase<sup>®</sup>, Yukinobu Watanabe<sup>®</sup>, Shin-Ichiro Abe<sup>®</sup>, Wang Liao<sup>®</sup>, *Member, IEEE*, Motonobu Tampo, Soshi Takeshita, Koichiro Shimomura, Yasuhiro Miyake, and Masanori Hashimoto<sup>®</sup>, *Senior Member, IEEE*

Abstract—We investigated the effects of positive and negative muons on 12-nm FinFET static random access memories (SRAMs) and 28-nm planar SRAMs and register files (RFs). For 12-nm devices, negative muons led to larger single-event upset (SEU) cross sections in two-fin or smaller cells, while positive muons showed a weaker dependence on the number of fins, with SEU cross sections increasing as cell area decreased. Similar trends were observed in 28-nm devices, where SRAM exhibited a higher SEU cross section under positive muons, while RF showed a larger SEU cross section under negative muons. Simulations reproduced experimental results for positive muons using a conventional single-sensitive volume (SSV) method, but negative muons posed challenges due to nuclear species with different linear energy transfer (LET) values. Standard SSV and multiple-sensitive volume (MSV) models failed to align with experimental data, but an approximation assigning separate critical charge  $(Q_c)$  values for muon direct ionization and secondary-ion ionization successfully reproduced the results, highlighting the need for particle-specific sensitive volume (SV)

Index Terms—FinFET, muons, single-event upset (SEU), soft errors, static random access memory (SRAM).

Received 29 December 2024; revised 30 January 2025; accepted 10 February 2025. Date of publication 14 February 2025; date of current version 18 August 2025. This work was supported by the Grant-in-Aid for Scientific Research (S) from Japan Society for the Promotion of Science (JSPS) under Grant JP19H05664 and Grant 24H00073. (Corresponding author: Yuibi Gomi.)

Yuibi Gomi, Kazusa Takami, Ryuichi Yasuda, and Masanori Hashimoto are with the Department of Informatics, Kyoto University, Kyoto 606-8501, Japan (e-mail: gomi.yuibi.48a@st.kyoto-u.ac.jp; hashimoto@i.kyoto-u.ac.jp).

Rurie Mizuno is with the Department of Physics, The University of Tokyo, Tokyo 113-0033, Japan.

Megumi Niikura is with the RIKEN Nishina Center for Accelerator-Based Science, Saitama 351-0198, Japan.

Yifan Deng, Shoichiro Kawase, and Yukinobu Watanabe are with the Faculty of Engineering Sciences, Kyushu University, Fukuoka 816-8580, Japan.

Shin-Ichiro Abe is with Japan Atomic Energy Agency (JAEA), Tōkai 319-1195, Japan.

Wang Liao is with the School of Systems Engineering, Kochi University of Technology, Kami 782-8502, Japan.

Motonobu Tampo, Soshi Takeshita, Koichiro Shimomura, and Yasuhiro Miyake are with the Muon Science Laboratory, High Energy Accelerator Research Organization (KEK), Tōkai 319-1106, Japan, and also with the Muon Section, Materials and Life Science Division, Japan Proton Accelerator Research Complex Center, Naka-gun 319-1195, Japan.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TNS.2025.3542468.

Digital Object Identifier 10.1109/TNS.2025.3542468

#### I. INTRODUCTION

SOFT errors, which are transient failures caused by radiation exposure from the surrounding environment, pose a significant challenge to device reliability. Addressing this issue has led to design efforts aimed at minimizing the error rate. Characterizing these errors is crucial for developing circuit design strategies to mitigate them. However, the study of muon-induced soft errors in terrestrial settings remains underexplored even though reports indicate that as semiconductor technologies evolve, the incidence of muon-induced soft errors tends to increase [1], [2]. To further our understanding of these errors in FinFETs, we have conducted experiments involving negative muon irradiation on FinFETs [3].

Our preliminary report [3] presents the first experimental data on negative muon-induced single-event upsets (SEUs) in 12-nm FinFET devices. These tests were conducted at the Muon Science Facility (MUSE) at the Japan Proton Accelerator Research Complex (J-PARC) [4], [5]. We compared the effects of both positive and negative muon irradiation on 12-nm FinFET and 28-nm planar static random access memory (SRAM) devices. The results confirmed that negative muons induce significantly higher SEU cross sections in FinFETs, consistent with previous findings in planar technologies. Moreover, this study highlights the differences between planar and FinFET technologies in terms of their susceptibility to muon-induced SEUs, providing valuable insights into the reliability challenges posed by muons in contemporary and future semiconductor devices.

However, the results presented in [3] were preliminary and did not include a detailed analysis of SEU cross sections for individual SRAM cell types. It has been suggested that advanced devices can exhibit significant variability in SEU sensitivity depending on the cell type [6], [7], [8]. Thus, there is a clear need to compare SEU cross sections for each cell type under both positive and negative muon irradiation. Furthermore, simulations to replicate the experimental results were not included in [3]. By conducting simulations to match the experimental data, this study aims to provide deeper insights into muon-induced SEUs and predict future

trends in SEU rates as technology nodes continue to scale down.

In this article, we analyze the differences in SEU cross sections among various cell types in terms of the number of fins and cell density for FinFET SRAMs compared to conventional planar FETs. We then perform Monte Carlo simulations to reproduce the measurement results. While the simulations for positive muons align well with the experimental data, we encounter a challenge with the critical charge  $(Q_c)$  in reproducing the results, as it differs between positive and negative muons in both single-sensitive volume (SSV) and multiple-sensitive volume (MSV) frameworks. This inconsistency arises because negative muon capture produces particles with a wide range of linear energy transfer (LET) values, requiring consideration of both small LET from muon direct ionization and large LET from secondary heavier ions, while only direct ionization induces SEUs in the case of positive muons. To address this diverse LET issue, we propose an approximation method to allocate two  $Q_c$  values: one for small LET particles of electrons and directly-ionizing muons, and another for protons, alpha particles, and heavier ions.

# II. RELATED WORK

Studies of muon-induced soft errors in terrestrial environments are still a relatively new field, especially compared to the well-established research on neutron-induced errors. As device scaling continues, the susceptibility of semiconductor technologies to radiation-induced soft errors increases, and the role of muons in these failures may become more pronounced. Traditionally, neutrons have been regarded as the primary contributors to soft errors in terrestrial environments, particularly due to their interaction with silicon nuclei. However, recent studies have shown that muons, which are abundantly present at ground level due to cosmic rays, also play an important role in causing soft errors in advanced semiconductor devices.

The occurrence of SEUs is driven by the deposition of electric charge near a transistor, which can alter its state. The minimum amount of charge required to induce a bit flip is referred to as  $Q_c$ . Muons, which can be either positively or negatively charged, contribute to SEUs through two primary mechanisms: 1) direct ionization caused by the muons themselves and 2) the generation of secondary ions during the negative muon capture reactions. Negative muons are more effective at inducing SEUs compared to their positive counterparts due to the production of protons, alpha particles, and heavy ions during the capture process. Based on Geant4 and SRIM simulations, the LET of secondary particles generated during negative muon capture significantly exceeds that of positive muons. For instance, while the LET of positive muons in silicon is approximately 0.5 MeV·cm<sup>2</sup>/mg even at the Bragg peak, alpha particles and heavy ions generated via negative muon capture exhibit substantially higher LET values [9]. This disparity in LET clearly demonstrates that secondary ions generated during negative muon capture have a much higher energy deposition capability, which greatly enhances charge deposition and increases the likelihood of SEUs.

Sierawski et al. [1] first demonstrated that positive muons could induce soft errors in CMOS SRAM memory at 65-, 45-, and 40-nm process nodes. Their results revealed that the contribution of positive muons to the soft error rate (SER) becomes more significant as technology scales down. This finding was corroborated by Seifert et al. [10], who reported similar trends in FinFET devices, with positive muon-induced SEUs observed across multiple FinFET process nodes. These studies established that positive muons, previously thought to have minimal impact at the sea level, are increasingly problematic for scaled technologies.

In contrast to positive muons, negative muons pose an even greater challenge due to their ability to undergo nuclear capture reactions. This process produces secondary particles with high LET, which, in turn, can induce SEUs with a much higher probability. Early studies by Liao et al. [11] and Manabe et al. [12] showed that negative muon-induced SEUs in 65-nm bulk and silicon on insulator (SOI) SRAMs had much larger cross sections than those induced by positive muons. This increased cross section is directly related to the high LET of the secondary ions generated during the negative muon capture reaction. These pioneering studies provided a crucial foundation for understanding the impact of negative muons on soft errors in modern semiconductor technologies.

Following these findings, further research extended the analysis to more advanced nodes. The SEU cross section induced by negative muons was evaluated for 28-nm planar SRAMs by Liao et al. [2], where similar trends were observed, with negative muons inducing significantly higher SEU cross sections compared to positive muons. This pattern was further confirmed in 20-nm SRAM technologies, highlighting the need to consider negative muons as a critical factor in soft error mitigation strategies for advanced process nodes [13].

Despite the growing body of work on muon-induced SEUs in planar technologies, research on their effects on FinFET devices has been limited. While some initial studies on positive muon-induced SEUs in FinFETs have been conducted [10], negative muon irradiation data for FinFETs have not been available in the literature until our preliminary report [3]. The unique 3-D structure of FinFETs introduces complexities in charge collection that may influence SEU mechanisms compared to planar devices. Thus, it is crucial to investigate how negative muons interact with FinFET structures, particularly at advanced nodes.

Previous studies have extensively investigated alpha and neutron-induced single-event reliability in SRAMs, offering valuable insights into radiation effects in advanced technologies [6], [14], [15], [16], [17], [18], [19], [20], [21], [22]. Many of these references report irradiation tests on either planar or FinFET SRAM technologies, examining alpha- and neutron-induced SEU cross sections across various energies, as well as analyzing multiple-cell upset (MCU) distributions. In addition, detailed simulations and in-depth analyses were conducted to replicate experimental results and provide a deeper understanding of radiation-induced phenomena.

Focusing more specifically on bulk FinFET SRAMs, Lee et al. [6] demonstrated that in 14-nm bulk FinFET SRAMs, high-performance (HP; two-fin) cells exhibited

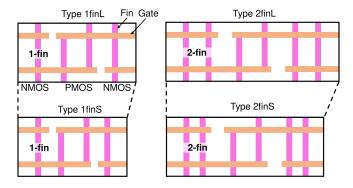

Fig. 1. Four types of FinFET SRAM cells.

higher alpha- and neutron-induced SERs compared to high-density (HD; one-fin) cells due to differences in charge collection efficiency driven by geometric isolation. Similarly, Uemura et al. [21] investigated alpha-induced SER in 4-nm bulk FinFET SRAMs and found that reducing the number of fins from 2 to 1 significantly lowered alpha-induced SER by 54%. These findings highlight how cell design parameters, such as fin count and sensitive volume (SV), influence radiation-induced SER in advanced nodes. While these studies focus on alpha and neutron radiation, they establish important benchmarks for comparing the effects of muons in similar technologies.

# III. EXPERIMENTAL RESULTS AND DISCUSSION

We conducted muon irradiation experiments on 12-nm FinFETs, 28-nm planar SRAMs, and 28-nm register file (RF) at the D2 experimental area of the J-PARC Muon Facility, MUSE [3]. The irradiation target chips, fabricated using a 12-nm process node, are equipped with four different types of SRAMs. The differences among these 12-nm FinFET types lie in the number of fins and the area of the memory cells. The chips fabricated using a 28-nm process include one type of SRAM and one type of RF. The RF test structure was implemented to allow data readout in a manner similar to the SRAM, enabling straightforward testing under the same conditions. The RF intellectual property (IP) was provided by the foundry. The 12-nm chip has a total bit size of 28.3 Mb, distributed equally among the four cell types (1finS, 1finL, 2finS, and 2finL), each having 7.08 Mb. For the 28nm chip, the total bit size is 18.9 Mb, with the SRAM accounting for 14.2 Mb and the RF accounting for 4.72 Mb. The SEU measurements were conducted under ambient room temperature conditions. The tests were performed in a static state, with no clock signal applied during the hold operation.

Fig. 1 illustrates the four types of 12-nm SRAM cells, which are named based on the number of fins and cell area (1finL, 2finL, 1finS, and 2finS). Each type can have either one or two fins and either a large or small cell area. Types 1finL and 1finS include one-fin transistors, while types 2finL and 2finS include two-fin transistors. Type 1finS has a smaller memory cell size than type 1finL, and type 2finS has a smaller memory cell size than type 2finL. The area differences between S and L are on the order of several percent, while the differences between 1fin

and 2fin range from about 20% to 30%. The 28-nm RF and SRAM both provide a one-port read/write function, but the RF is optimized for speed, while the SRAM is designed for area efficiency. Though both use a six-transistor (6T) structure, the nMOS transistors in RF are larger than those in SRAM to enhance read/write speed. The area ratio of the 28-nm SRAM to the RF cells is 1.2–1.3.

For 12-nm devices, we conducted momentum scans and found that the SEU cross section peaked near a muon momentum of 33.9 MeV/c, with operation voltages supplied at 0.30, 0.56, and 0.69 V. The SEU cross section is maximized when large charge deposition occurs near the transistors corresponding to the Bragg peak of charged particle energy deposition [9]. Since muons are charged particles, they lose energy as they penetrate the device. The Bragg peak, where the energy loss is greatest just before stopping, was found near the transistors to occur for muons with an initial momentum of approximately 33.9 MeV/c in our device under test (DUT) setup with a resin package. Muons with momentum lower than this value cannot reach the transistors, while muons with higher momentum pass through the vicinity of the transistors without depositing significant energy, resulting in a peak in the SEU cross section as a function of momentum. In addition, secondary particles generated through negative muon capture contribute significantly to the SEU cross section. In particular, the secondary particles produced near the transistors have larger solid angles relative to the SVs, increasing the likelihood of reaching the SVs and depositing energy. This mechanism enhances the probability of charge collection, further amplifying the observed SEU cross section near the Bragg peak for certain particle interactions. Similarly, for 28-nm devices, the scans were performed at an operation voltage of 0.77 V.

# A. SEU Cross Sections

In this study, the term "SEU cross section" refers to the momentum-averaged cross section, as the muon beams used in the experiments exhibit momentum distributions.

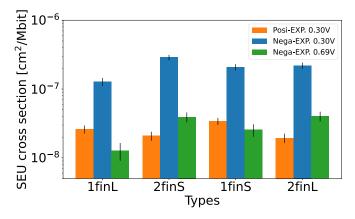

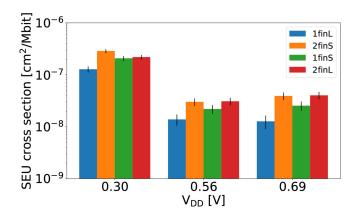

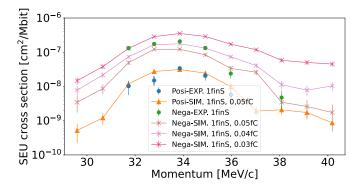

Fig. 2 shows muon-induced SEU cross sections at the momentum of 33.9 MeV/c, including results for 0.30 V with positive muons and 0.30 and 0.69 V with negative muons, where no SEUs are observed for positive muons at 0.69 V.

First, we focus on the negative muon case. The SEU cross section for negative muons is the largest in type 2finS, followed by types 2finL, 1finS, and 1finL, in this order. When considering the cell area, we observe that type 1finS, which has a smaller area, exhibits larger SEU cross sections than 1finL. In the two-fin types, 2finS shows a larger SEU cross section than 2finL. Regarding the number of fins, 2finL and 2finS exhibit larger SEU cross sections than 1finL and 1finS, respectively. In addition, the trend of larger SEU cross sections for configurations with two fins or smaller cell areas is also observed in alpha irradiation of 4-nm FinFET SRAMs [21]. Similarly, neutron-induced SEU cross sections in 14-nm FinFET SRAMs also exhibit this trend with HP cells showing larger SEU cross sections compared to HD cells [6].

The variation in the SEU cross section caused by negative muons depending on the cell type can be attributed to a

Fig. 2. Positive and negative muon-induced SEU cross sections measured in the experiments at the momentum of 33.9 MeV/c and 12-nm four-type SRAM chips operated at voltages of 0.30 and 0.69 V. The cell type names indicate the number of fins ("1fin" or "2fin") and the cell size ("S" for small and "L" for large).

balance between the SV size and the  $Q_c$ . For two-fin cells, the larger SV allows for more charge collection, making them more susceptible to bit flips. Conversely, two-fin cells have a higher  $Q_c$ , which reduces the likelihood of bit flips for the same amount of collected charge. These opposing effects influence the SEU cross section, and their balance determines the relative likelihood of bit flips between one- and twofin cells. Similarly, the cell size also plays a critical role. Previous studies on alpha particle irradiation in 4-nm FinFET SRAMs have shown that smaller cells exhibit higher SEU cross sections. This has been attributed to shorter fin pitches, resulting in shallower shallow trench isolation (STI) regions and larger SVs. However, for 12-nm technologies, to the best of our knowledge, no reports indicate a reduction in STI depth. Therefore, alternative factors could be contributing to this trend. One possible explanation is that while the SV size remains the same, the reduced cell area increases the relative proportion of the SV to the cell area, leading to higher SEU cross sections. Another contributing factor could be the decreased distance between fins in smaller cells, which might increase the likelihood of simultaneous charge deposition across multiple transistors, thereby enhancing the probability of a bit flip. However, we note that the literature comparing SEU cross sections between SRAMs with the same fin count but different cell sizes is currently limited.

On the other hand, the SEU cross sections for positive muons decrease in the order of 1finS, 1finL, 2finS, and 2finL. This indicates that the smaller the cell area, the larger the SEU cross section. Compared to alpha particles and heavy ions, which can be generated through negative muon capture reactions, positive muons exhibit a lower LET. Based on LET data simulated using Geant4 and SRIM, the maximum LET of positive muons in silicon is about 0.5 MeV·cm²/mg at the Bragg peak of 5 keV, and the LET decreases to 0.06 MeV·cm²/mg at 500 keV. Even at the Bragg peak, the LET of positive muons is lower than the LET values of half the alpha particles and most heavy ions that are produced by the muon capture reactions [9]. These differences highlight the relatively lower energy deposition capabilities of positive

Fig. 3. Positive and negative muon-induced SEU cross sections measured in the experiments at the momentum of 33.9 MeV/c and 28-nm RF and SRAM chips operated at a voltage of 0.77 V.

muons. Although the two-fin cell has a larger sensitive area, which typically increases the likelihood of generating SEUs, it also shows an increase in parasitic capacitance, which raises the critical charge and, consequently, reduces the SEU cross section. For positive muons with low LET, the larger parasitic capacitance of the two-fin cell predominates, resulting in a smaller SEU cross section compared to the one-fin design. However, this observation is in contrast to experimental results from neutron and alpha particle irradiation, where two-fin cells exhibited larger SEU cross sections than one-fin cells [6], [21].

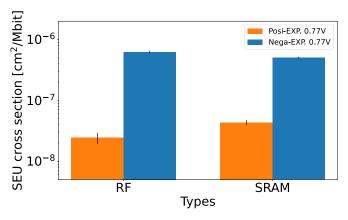

Fig. 3 shows the SEU cross sections induced by positive and negative muons at a momentum of 33.9 MeV/c for 28-nm devices operating at 0.77 V. SEU cross sections are compared between RF and SRAMs for both positive and negative muon cases. In this comparison, the diffusion and parasitic capacitance of the 28-nm SRAMs are smaller than that of RF and correspond to those of the one- and two-fin designs in the 12-nm devices, respectively. For positive muons, the small-capacity SRAMs exhibit a larger SEU cross section, while, for negative muons, the large-capacity RF is more sensitive.

# B. SEU Dependency on Operating Voltage

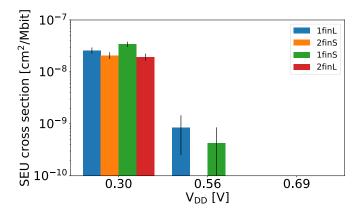

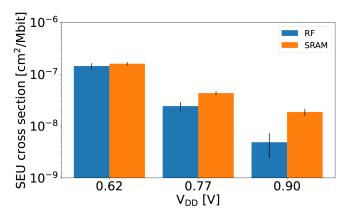

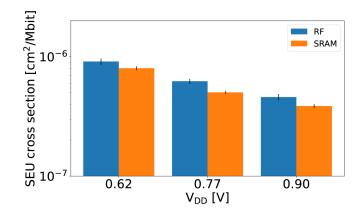

Figs. 4 and 5 show the positive and negative muon-induced SEU cross sections at 33.9 MeV/c of 12-nm SRAMs as a function of operating voltage, respectively. Note that the 12-nm cross sections at 0.56 V are for 32.8 MeV/c due to data missing. Although the data at 32.8 MeV/c were obtained due to an experimental setup error, it remains valid for analysis, as explained in the following. At 0.30 V, the SEU cross sections for all cell types, except for the positive muon 1finS and negative muon 2finS cases, show similar values between the measurements of 33.9 and 32.8 MeV/c, with data points falling within the statistical error margins, which will be found later in Section IV-B. This suggests that the slight momentum difference does not significantly affect the SEU cross sections for most cell types. Therefore, the 32.8-MeV/c data can be reliably used for further analysis without compromising the overall conclusions. There is no plot of 12-nm positive muon

Fig. 4. 12-nm SEU cross sections versus operating voltage under positive muon irradiation at 33.9 MeV/c. At 0.56 V, the beam momentum is 32.8 MeV/c.

Fig. 5. 12-nm SEU cross sections versus operating voltage under negative muon irradiation at 33.9 MeV/c. At 0.56 V, the beam momentum is 32.8 MeV/c.

since no upset was observed in 1-h irradiation of 33.9-MeV/c positive muons at 0.69 V.

For negative muons, the same order of SEU cross sections by type observed at 0.30 V is mostly maintained at 0.56 and 0.69 V, showing consistent trends across operating voltages. However, at 0.56 V, the 2finS data were measured at 32.8 MeV/c, resulting in a slightly different trend for this type. When comparing the power supply voltage dependence between positive and negative muons, the SEU cross sections for positive muons increase more rapidly as the voltage decreases compared to those for negative muons. This trend suggests that as process technology continues to scale down, the SEU cross sections for positive muons may increase sharply, indicating greater sensitivity in more advanced technologies.

Figs. 6 and 7 show the positive and negative muon-induced SEU cross sections at 33.9 MeV/c for 28-nm RF and SRAM devices as a function of operating voltage, respectively. For positive muons, the SEU cross sections of SRAMs are larger than those of the RF at all operating voltages, consistent with the trend observed in the 12-nm devices. In the case of 12-nm devices, the SEU cross sections for the one-fin type, which has a smaller parasitic capacitance, are larger than those for the two-fin type under positive muon irradiation,

Fig. 6. 28-nm SEU cross sections versus operating voltage under positive muon irradiation at 33.9 MeV/c.

Fig. 7. 28-nm SEU cross sections versus operating voltage under negative muon irradiation at 33.9 MeV/c.

while the opposite trend is observed for negative muons. This corresponds to the behavior in 28-nm devices, where SRAM with smaller parasitic capacitance behaves similar to the one-fin type and RF corresponds to the two-fin type, demonstrating consistency in the results across different technologies. As the operating voltage increases, the SEU cross sections for both SRAMs and RF decrease. For negative muons, a similar trend is observed across all operating voltages, where the SEU cross sections of the RF are larger than those of the SRAM. This trend is consistent regardless of the operating voltage, indicating that the RF remains more susceptible to SEUs in negative muon irradiation at all voltage levels.

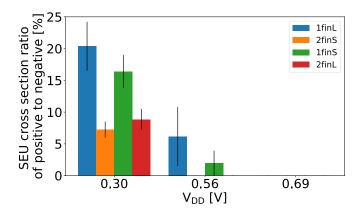

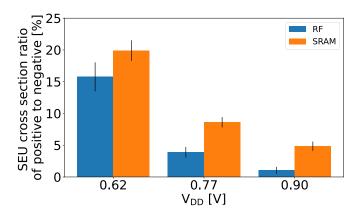

Fig. 8 shows the SEU cross section ratio of positive muons to negative muons for 12 nm. This indicator is a measure of the percentage of SEUs produced by muon direct ionization out of all SEUs, including those due to secondary ions produced by negative muon nuclear capture reactions. In the 12-nm SRAMs at 0.30 V, the ratio of two-fin FinFET designs is significantly smaller than that of one-fin designs. This result suggests that one-fin designs fabricated in more advanced technology nodes with less critical charge could be more sensitive to muon direct ionization.

Fig. 9 shows the ratio of positive muon-induced SEU cross sections to those of negative muons for 28 nm. While the ratio is slightly higher for the SRAMs compared to RF at a low voltage of 0.62 V, the difference is not significant.

Fig. 8. Ratio of positive muon-induced SEU cross section to that of negative muons for 12 nm. The muon momentum is 32.8 MeV/c for 12-nm FinFETs at 0.56 V and 33.9 MeV/c for the others.

Ratio of the positive muon-induced SEU cross section to that of negative muons for 28 nm. The muon momentum is 33.9 MeV/c.

TABLE I SEU CROSS SECTION COMPARISON BY CELL TYPES FOR 12-nm FINFET AND 28-nm PLANAR DEVICES

| 12 nm                |                                   |

|----------------------|-----------------------------------|

| Condition            | SEU CS Order by Cell Type         |

| Positive Muon, 0.69V | No SEUs                           |

| Positive Muon, 0.30V | 1 finS > 1 finL > 2 finS > 2 finL |

| Negative Muon, 0.69V | 2 finS > 2 finL > 1 finS > 1 finL |

| Negative Muon, 0.30V | 2 finS > 2 finL > 1 finS > 1 finL |

| 28 nm                |                                   |

| Positive Muon, 0.90V | SRAM > RF                         |

| Positive Muon, 0.62V | SRAM > RF                         |

| Negative Muon, 0.90V | RF > SRAM                         |

| Negative Muon, 0.62V | RF > SRAM                         |

As the voltage increases, the ratio decreases gradually for both SRAMs and RF. Although there is a difference between RF and SRAM, it is not as pronounced as the differences observed between two- and one-fin types in 12-nm devices.

# C. Comparison Summary

Table I presents the summary of the SEU cross section comparison for various cell types in 12-nm FinFET and 28-nm planar devices under positive and negative muon irradiation. The SEU cross section trends are analyzed at high and low supply voltages for both technologies.

For 12-nm FinFET devices, under positive muon irradiation at a low voltage of 0.30 V, the 1finS type exhibits the highest

SEU cross section, followed by 1finL, 2finS, and 2finL. This indicates that cells with smaller parasitic capacitance, such as 1finS, are more vulnerable to soft errors in these conditions. Conversely, under negative muon irradiation, the 2finS type shows the highest SEU cross section at both high and low voltages. This trend highlights the increased sensitivity of cells with larger SVs under negative muon irradiation.

For 28-nm planar devices, SRAM shows higher SEU cross sections than RF under positive muon irradiation at both high (0.90 V) and low (0.62 V) voltages. In contrast, under negative muon irradiation, the SEU cross section of RF becomes comparable to or even larger than that of SRAM at both voltage levels. This suggests that the sensitivity of RF to negative muons increases relative to SRAM, particularly at lower voltages. These results indicate that the cell architecture and the type of muon irradiation play significant roles in determining SEU susceptibility across different technologies and voltage levels.

# D. FIT Rate in 12-nm SRAM

Using the energy spectra of positive and negative muons in terrestrial environments obtained from Excel-based program for calculating atmospheric cosmic-ray spectrum (EXPACS), the failure-in-time (FIT) rates near the peak momentum were calculated for the 1finL configuration at 0.30 V. The FIT rate was determined to be 0.020 FIT/Mb for positive muons and 0.123 FIT/Mb for negative muons.

For comparison, neutron irradiation experiments conducted at the Research Center for Nuclear Physics (RCNP) using the same device yielded an FIT rate of 18.9 FIT/Mb at 0.45 V. In contrast, the FIT rates calculated for muons near the peak momentum, 0.020 FIT/Mb for positive muons and 0.123 FIT/Mb for negative muons, are significantly smaller. These results indicate that muons contribute only a very small fraction to the overall SEU rate under typical terrestrial conditions when considering only the peak momentum. However, it is well known that muons can penetrate materials more deeply than neutrons, which can result in a higher relative ratio of muon-induced SER in environments such as buildings or underground facilities, where neutrons are comparatively fewer. More importantly, in terrestrial environments, most muons possess energies significantly greater than those near the peak momentum. Although the SEU cross section at these higher energies is very small, their contribution must still be taken into account for a comprehensive analysis of the total SEU rate.

# IV. SIMULATION OF MUON-INDUCED SEUS

## A. Method

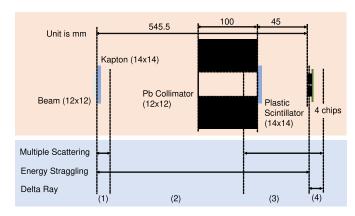

Muon-induced SEUs in four types of 12-nm FinFETs and 28-nm RF, SRAMs were simulated using the particle and heavy ion transport code system (PHITS) ver. 3.26 [23]. A 3-D model, replicating the experimental setup, was constructed, and muons were virtually irradiated onto the system. The momentum spread is assumed to follow a Gaussian distribution, with its standard deviation set at 4%. Fig. 10 shows the simulation system, which largely replicates the experimental setup of the muon irradiation. Authorized licensed use limited to: Kyoto University. Downloaded on October 05,2025 at 02:38:47 UTC from IEEE Xplore. Restrictions apply.

Fig. 10. PHITS simulation setup and used simulation options in each subregion.

The thicknesses of the Kapton film and plastic scintillator are 0.1 and 0.5 mm, respectively. On the other hand, the number of chips and the size of the collimator holes have been modified to enhance simulation efficiency while maintaining compatibility with the experimental setup.

1) Simulation Speedup: In simulations, there are two primary challenges: 1) slow simulation speeds and 2) the exclusiveness of simulation options. In this work, to address the issue of simulation speed, we divided the simulation region into four subregions (1)-(4), as shown in Fig. 10. The simulations in subregions are carried out sequentially from the upstream to the downstream. The dumped particles in one subregion are passed to the downstream subregion. We selectively applied simulation options for multiple scattering, energy straggling, and delta-ray generation to each region to accelerate the simulation while accurately reproducing the physical phenomena that are crucial in each subregion. Here, multiple scattering is an option that considers the angle of scattering upon entry. Energy straggling introduces randomness in the energy loss per unit length. Delta-ray generation represents particle energy loss through the transport of delta rays. It is important to note that the energy straggling and delta-ray generation options cannot be enabled simultaneously, as they both model the same type of energy loss but in different ways.

The energy distribution of the muons after passing through the Kapton film is simulated in subregion (1). In (2), the 12 × 12 mm beam is regenerated and transported according to the energy distribution obtained in (1). The simulation efficiency in (2) is improved by omitting the multiple scattering options due to the thick air layer, which prevents most muons from reaching the chips. It is important to note that the number of muons reaching the chips is counted by the plastic scintillator; therefore, omitting the multiple scattering in (2) does not compromise the estimation accuracy of the SEU cross section. In (3), similar to (1), options for multiple scatterings and energy straggling are used to transport the muons to the front of the SV. The delta-ray generation option is employed in (4) to precisely reproduce the phenomena that deposit charges in the SRAM chips.

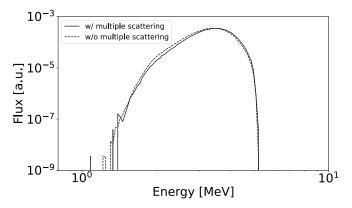

To validate this speedup method, Fig. 11 shows the energy spectra of positive muons at 33.9 MeV/c, measured just in front of the chip, with and without including multiple

Fig. 11. Energy spectra comparison with (solid line) and without (dashed line) multiple scattering in (2), simulated using positive muons at 33.9 MeV/c. Both spectra are normalized to match the peak flux.

Fig. 12. Constitution of the 12-nm SRAM board in PHITS simulation.

scattering effects in (2). The flux is measured directly in front of the chip and reflects the angular dispersion of the particles. The energy spectra for each setting were normalized at the peak energy to facilitate comparison. When multiple scattering is not considered, the energy spectrum shows a higher concentration of low-energy particles and a lower concentration of high-energy particles compared to the case where multiple scattering is included. However, the peak energy remains the same, and the overall shape of the spectrum does not change significantly. In addition, when multiple scattering is not considered, 11.8 times more particles reach the region just before the chip, which directly corresponds to the simulation speedup.

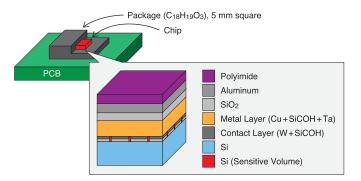

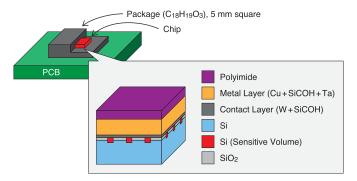

2) Device Modeling: Figs. 12 and 13 illustrate the constitution of the 12-nm SRAM board and the 28-nm RF and SRAM board used in the PHITS simulation. Both figures depict a cross-sectional view of the chip and its various layers, including the packaging and printed circuit board (PCB).

Fig. 12 includes a 12-nm SRAM chip mounted on a PCB with a 5-mm square package. The chip consists of several layers: a top layer of polyimide, followed by an aluminum layer, and various metal and contact layers (Cu + SiCOH + Ta and W + SiOCH), with an SiO<sub>2</sub> layer beneath. The SV is located in the silicon layer at the bottom. Fig. 13 depicts the 28-nm RF and SRAM board, also mounted on a 5-mm square package. The layer structure is similar to that of the 12-nm SRAM, with a polyimide layer on top, followed by metal and contact layers, and the silicon-SV at the bottom.

Fig. 13. Constitution of the 28-nm RF and SRAM board in PHITS simulation.

Fig. 14. Charge collection efficiency around an OFF-state nMOS transistor in a 12-nm FinFET SRAM, derived from TCAD simulations. The supply voltages for (a)–(c) are 0.45, 0.45, and 0.69 V, respectively, with corresponding deposited charge amounts of 0.05, 0.25, and 0.25 fC.

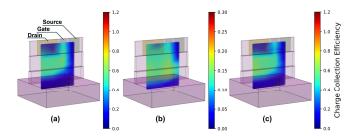

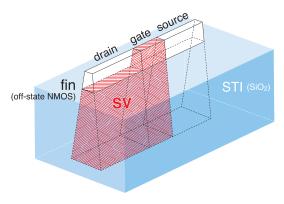

3) Sensitive Volume Modeling: In this work, we consider two types of SV models for 12-nm FinFETs: the SSV model, which assumes that 100% efficient charge collection occurs in a single localized region, and the MSV model, which accounts for location-dependent charge collection efficiencies in multiple spatially separated regions [24], [25].

Fig. 14 shows the charge collection efficiency in the fin, obtained through the technology CAD (TCAD) simulations [24], [26]. The simulation divided the fin into 24 segments and the bulk region into 16 segments, resulting in 40 segments in total where the charge collection efficiency for each segment was calculated. Then, the efficiency values between these points were linearly interpolated. The charge collection efficiency was calculated by placing a point charge at the center of each segment. It is important to note that only in Fig. 14(b), the maximum value of the scale is set to 0.3. The power supply voltage and the amount of deposited charge for Fig. 14(a)-(c) are 0.45, 0.45, and 0.69 V, with deposited charges of 0.05, 0.25, and 0.25 fC, respectively. Here, the charge collection efficiency was evaluated at 0.45 V instead of 0.30 V since the TCAD simulation did not converge at 0.30 V. The deposited charge of 0.05 fC represents the charge deposited by particles with low LET, while 0.25 fC corresponds to the charge deposited by high LET particles across the entire fin.

Fig. 15 shows the SSV assumed in this work for an OFF-state n-FinFET. An SV is a region where bit flips are likely to occur when charged particles deposit a certain amount of charge. In the following discussion, we assume that a bit flip occurs when the charge deposited into the SV exceeds a threshold value known as the critical charge  $(Q_c)$ . The SV was determined by TCAD simulations, as illustrated in Fig. 14(a), and the volume where the charge collection

Fig. 15. Location of the SSV in 12-nm FinFET SRAM for PHITS simulation.

efficiency exceeds 0.4 was selected as the SV. The SV for the two-fin devices was the same SV for each fin as the one-fin device. For 28-nm devices, a 500-nm deep SSV was applied to the bulk region corresponding to the OFF-state nMOS in the SRAM to model the charge collection process, and this was appropriately adjusted based on the SSV used for the 25-nm rule in [27].

The MSV model was constructed by assigning the collected charge in each segment according to the charge collection efficiency derived from the TCAD simulations in Fig. 14. As the charge collection efficiency in the bulk is very low, as shown in Fig. 14, the MSV was applied only to the fin. For the simulations at 0.30 and 0.69 V, the charge collection efficiencies from Fig. 14(a) and (c) were used, respectively.

# B. Simulation Results

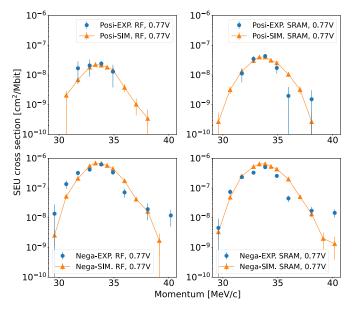

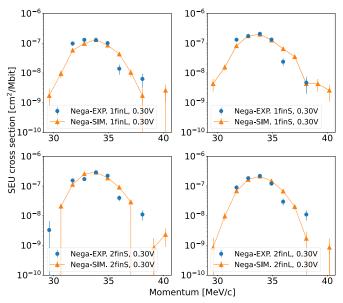

Positive and negative muon irradiation simulations were conducted on two types of 28-nm devices. Since the 28-nm devices, like the 65-nm devices [28], could reproduce the experimental results using the SSV model with the same  $Q_c$  for both positive and negative muons, the MSV model was not applied. For the 12-nm devices, positive and negative muon irradiation was performed on four types using the SSV model and on one-fin types using the MSV model. The MSV model could not be applied to the two-fin types due to the lack of a corresponding TCAD model. The error bars represent the standard error of the SEU cross section. These were calculated based on the statistical distribution of observed error counts during the experiments and simulations.

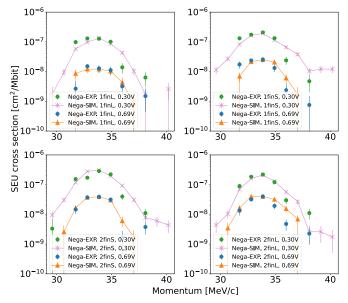

- 1) 28-nm SRAM and RF: Fig. 16 illustrates the momentum dependence of the positive and negative muon-induced SEU cross sections for 28-nm devices. In the simulation, we derived the  $Q_c$  for the SRAM and RF to ensure that the simulated SEU cross section at 33.9 MeV/c aligned with the measured data.  $Q_c$ , which reproduces the measurement result, was calculated separately for SRAM and RF, yielding values of 0.9 and 1.2 fC, respectively. These values reproduced the experimental data for both positive and negative muons successfully.

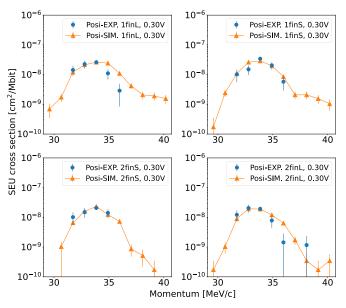

- 2) 12-nm SRAMs: Fig. 17 illustrates the momentum dependence of the SEU cross sections induced by positive muon irradiation for 12-nm devices using the SSV model. The simulations were conducted at a supply voltage of 0.30 V, and the SEU cross sections were compared with the experimental

Fig. 16. Simulation results of positive and negative muons irradiation for 28-nm SRAM and RF at 0.77 V.

Fig. 17. Positive muons irradiation simulation results for each type of 12-nm devices at 0.30 V using the SSV model.

data. The  $Q_c$  values that reproduce the measurement results with the SSV model were 0.1, 0.15, 0.1, and 0.16 fC for 1finL, 2finS, 1finS, and 2finL, respectively.

Fig. 18 shows the results of positive muon-induced SEU cross section simulations for 12-nm one-fin SRAMs using the MSV model. The  $Q_c$  values that reproduce the measurement data with the MSV model were 0.05 fC for both 1finL and 1finS.

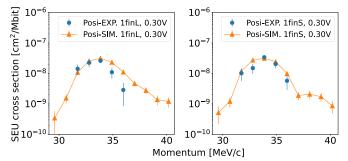

Similar evaluations are performed for negative muons with the SSV and MSV models. The results are found in Figs. 19 and 20. The  $Q_c$  values that reproduce the measurement results with the SSV model at a supply voltage of 0.30 V were 0.1, 0.09, 0.08, and 0.12 fC for 1finL, 2finS, 1finS, and 2finL, respectively. The  $Q_c$  values for the MSV model were 0.05 and 0.04 fC for 1finL and 1finS, respectively.

Fig. 18. Positive muons irradiation simulation results for each type of 12-nm devices using the MSV model.

Fig. 19. Negative muons irradiation simulation results for each type of 12-nm devices at 0.30 V using the SSV model.

Fig. 20. Negative muons irradiation simulation results for each type of 12-nm devices using the MSV model.

For the supply voltage of 0.69 V, the  $Q_c$  values with the SSV model were 0.46, 0.4, 0.32, and 0.36 fC for 1finL, 2finS, 1finS, and 2finL, respectively. The  $Q_c$  values for the MSV model at 0.69 V were 0.2 and 0.15 fC for 1finL and 1finS, respectively.

In the 12-nm SRAMs, a key challenge is the discrepancy in  $Q_c$  between positive and negative muons, while for the 28-nm planar SRAMs, simulations of both positive and negative muon irradiation have shown that experimental data can be reproduced using the same  $Q_c$  value, as shown in Fig. 16. Although the  $Q_c$  values for positive and negative muons differ regardless of whether the SSV or MSV model is used, the 1finL SRAM type can be reproduced using the same  $Q_c$  for

Fig. 21. Simulation results of the momentum dependence of SEU cross section for positive and negative muons and secondary ions at the same  $Q_c$  with the MSV model.

both positive and negative muons. However, as illustrated in Fig. 21, the same approach fails for 1finS at 0.30 V, where using the same  $Q_c$  for both positive and negative muons does not reproduce the experimental results. Similarly, for the 2finS and 2finL types, the  $Q_c$  values for positive and negative muons also do not match at 0.30 V, making it difficult to reproduce the experimental results for these types.

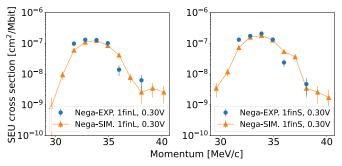

# C. Approximating Particle-Dependent SV as Particlewise Two $Q_c$ Values

Negative muons produce particles with significantly different LET values [29], making it challenging to reproduce experimental results for negative muon irradiation. This difficulty arises from applying the same SSV and MSV models to all particles. Comparing Fig. 14(a) and (b), it becomes clear that different charge amounts lead to distinct SSV shapes, and the charge collection efficiency values and distributions used for the MSV model vary significantly. This results in substantial variations in the SV configuration depending on the particle type. Thus, using the same SSV and MSV configurations across different charge amounts proves difficult for accurately simulating the experimental results.

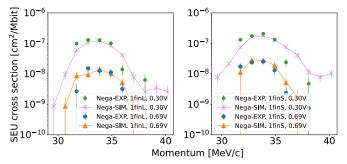

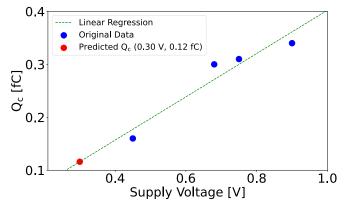

This difference in  $Q_c$  observed in Section IV-B suggests that the SV for direct ionization by positive and negative muons and the SV for secondary ions from the negative muon nuclear capture reaction could differ or that the  $Q_c$  values might vary. To approximately consider the particle and LET dependence, we propose an approximation method that distinguishes the  $Q_c$  for direct ionization by positive and negative muons and electrons  $(Q_{c1})$  from  $Q_c$  for secondary ions resulting from the negative muon capture reaction  $(Q_{c2})$ . Considering that the direct ionization effects of positive and negative muons are comparable, the  $Q_{c1}$  for negative muons was set to be the same as the  $Q_c$  for positive muons.

Fig. 22 shows that the measured SEU cross sections for all four SRAM types (1finL, 2finS, 1finS, and 2finL) are accurately reproduced using  $Q_{c1}$  and  $Q_{c2}$  values at 0.30 V with the SSV model. The  $Q_{c1}$  values for 1finL, 2finS, 1finS, and 2finL are 0.1, 0.15, 0.1, and 0.16 fC, respectively, while the reply  $Q_{c2}$  values are 0.1, 0.06, 0.05, and 0.09 fC, respectively.

To validate the appropriateness of the  $Q_{c2}$  value for the 1finL configuration, we analyzed experimental results from

Fig. 22. Negative muons irradiation simulation results for each type of 12-nm device using the SSV model. An approximation method using two different critical charge values,  $Q_{c1}$  for direct ionization and  $Q_{c2}$  for ionization caused by secondary ions, was applied to reproduce the experimental results.  $Q_{c1}$  and  $Q_{c2}$  are for 0.30 V.

Fig. 23. Critical charge  $(Q_c)$  as a function of supply voltage for the 1finL configuration. Blue points represent the original data obtained from neutron irradiation experiments, while the red point indicates the predicted  $Q_c$  value at 0.30 V (0.12 fC) derived using linear regression (green dashed line).

neutron irradiation performed at RCNP. The  $Q_c$  at 0.30 V was predicted to be 0.12 fC using linear regression based on the following measured data: 0.90 V: 0.34 fC, 0.75 V: 0.31 fC, 0.68 V: 0.30 fC, and 0.45 V: 0.16 fC. These values were extrapolated to 0.30 V, as shown in Fig. 23. The predicted value of 0.12 fC is reasonably consistent with the  $Q_{c2}$  value of 0.1 fC used in our SSV-based simulations for the 1finL configuration, demonstrating the validity of our estimation approach. It should be noted that this validation applies only to the 1finL configuration and the SSV model. Other configurations (1finS, 2finS, and 2finL) and the MSV model have not been validated against the RCNP results as the corresponding data remain unexamined.

Similarly, Fig. 24 demonstrates that the measured SEU cross sections for one-fin types are accurately reproduced with  $Q_{c1}$  and  $Q_{c2}$  values at 0.30 V using the MSV model. The  $Q_{c1}$  values for 1finL and 1finS are both 0.05 fC, while the  $Q_{c2}$  values are 0.05 and 0.03 fC, respectively. Thanks to the

Fig. 24. Negative muons irradiation simulation results for each type of 12-nm device using the MSV model. An approximation method using two different critical charge values,  $Q_{c1}$  for direct ionization and  $Q_{c2}$  for ionization caused by secondary ions, was applied to reproduce the experimental results.  $Q_{c1}$  and  $Q_{c2}$  are for 0.30 V.

Fig. 25. Contribution of secondary ions to SEU for type 1finL with the MSV model.

additional  $Q_c$  parameter, the experimental results are well reproduced.

Our future work will involve a more comprehensive analysis of particle and LET-dependent SV and  $Q_c$ , and the development of a generalized approximation method applicable to both FinFET and Planar FET structures. One possible direction is the implementation of a machine learning-assisted classifier [30], [31].

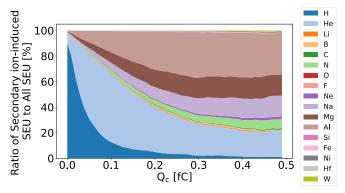

# D. Secondary Ions Contributing to SEU

Fig. 25 illustrates the decomposition of secondary ions produced by negative muon nuclear capture reactions contributing to SEUs in type 1finL at 33.9 MeV/c. As  $Q_c$  decreases, lighter ions become more dominant. At 0.05 fC, corresponding to 0.30-V operation with MSV, the alpha particles comprise approximately 50%, while at 0.2 fC (0.69 V), the sum of Na, Mg, and Al ions accounts for approximately 50%.

Technology scaling, along with voltage reduction, will decrease  $Q_c$  values. Protons account for approximately 50% at a  $Q_c$  of 0.03 fC. Due to their lighter mass, protons can travel longer distances. Consequently, negative muon capture reactions occurring even at locations distant from transistors can cause SEUs.

### V. CONCLUSION

We analyzed the effects of positive and negative muons on different cells in 12-nm FinFET SRAM and 28-nm planar SRAM and RF. For 12-nm devices, negative muons induced larger SEU cross sections in two-fin cells or smaller cells when the number of fins was constant. However, this effect was less pronounced with positive muons, where the SEU cross section increased as the cell area decreased. In the case of 28-nm devices, the SEU cross section of the SRAM, whose cell is smaller than that of RF, was larger than that of the RF under positive muon irradiation, while, under negative muon irradiation, the SEU cross section of the RF was larger. This trend is similar to the relationship observed in the SEU cross sections of one- and two-fin cells in the 12-nm devices.

Simulations for positive muon irradiation were successfully conducted for both 12- and 28-nm devices, and the experimental results were accurately reproduced in the conventional method. However, for negative muons, the presence of nuclear species with significantly different LET values made it impossible to reproduce the experimental results using the same  $Q_c$  as positive muons, even with SSV and MSV models constructed based on TCAD simulations. As an approximation,  $Q_c$  for negative muons was separately set for direct ionization and ionization by secondary ions, which allowed for accurate reproduction of the experimental results.

#### ACKNOWLEDGMENT

This muon experiment was performed with technical staff support at the Materials and Life Science Experimental Facility of the J-PARC under user program No. 2022B0197.

# REFERENCES

- B. D. Sierawski et al., "Muon-induced single event upsets in deepsubmicron technology," *IEEE Trans. Nucl. Sci.*, vol. 57, no. 6, pp. 3273–3278, Dec. 2010.

- [2] W. Liao et al., "Negative and positive muon-induced SEU cross sections in 28-nm and 65-nm planar bulk CMOS SRAMs," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2019, pp. 396–400.

- [3] Y. Gomi et al., "Muon-induced SEU cross sections of 12-nm FinFET and 28-nm planar SRAMs," in *Proc. 23rd Eur. Conf. Radiat. Effects Compon. Syst. (RADECS)*, Sep. 2023, pp. 27–30.

- [4] Y. Miyake et al., "J-PARC muon facility, MUSE," *Phys. Proc.*, vol. 30, pp. 46–49, Jun. 2012.

- [5] Y. Miyake et al., "Current status of the J-PARC muon facility, MUSE," J. Phys., Conf., vol. 551, Dec. 2014, Art. no. 012061.

- [6] S. Lee et al., "Radiation-induced soft error rate analyses for 14 nm FinFET SRAM devices," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2015, pp. 360–363.

- [7] T. S. Copetti, G. C. Medeiros, M. Taouil, S. Hamdioui, L. M. B. Poehls, and T. R. Balen, "Evaluation of single event upset susceptibility of FinFET-based SRAMs with weak resistive defects," *J. Electron. Test.*, vol. 37, pp. 383–394, Jun. 2021.

- [8] A. S. Sajit and M. A. Turi, "SEU tolerance of FinFET 6T SRAM, 8T SRAM and DICE memory cells," in *Proc. IEEE Annu. Comput. Commun. Workshop Conf. (CCWC)*, Jan. 2017, pp. 313–317.

- [9] J.-L. Autran and D. Munteanu, "Interactions of low-energy muons with silicon: Numerical simulation of negative muon capture and prospects for soft errors," J. Nucl. Eng., vol. 5, no. 1, pp. 91–110, Mar. 2024.

- [10] N. Seifert, S. Jahinuzzaman, J. Velamala, and N. Patel, "Susceptibility of planar and 3D tri-gate technologies to muon-induced single event upsets," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2015, pp. 50–55.

- [11] W. Liao et al., "Measurement and mechanism investigation of negative and positive muon-induced upsets in 65-nm bulk SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 8, pp. 1734–1741, Aug. 2018.

- [12] S. Manabe et al., "Negative and positive muon-induced single event upsets in 65-nm UTBB SOI SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 8, pp. 1742–1749, Aug. 2018.

- [13] T. Kato et al., "Muon-induced single-event upsets in 20-nm SRAMs: Comparative characterization with neutrons and alpha particles," *IEEE Trans. Nucl. Sci.*, vol. 68, no. 7, pp. 1436–1444, Jul. 2021.

- [14] P. Roche, G. Gasiot, K. Forbes, V. O'Sullivan, and V. Ferlet, "Comparisons of soft error rate for SRAMs in commercial SOI and bulk below the 130-nm technology node," *IEEE Trans. Nucl. Sci.*, vol. 50, no. 6, pp. 2046–2054, Dec. 2003.

- [15] E. Ibe, H. Taniguchi, Y. Yahagi, K. Shimbo, and T. Toba, "Impact of scaling on neutron-induced soft error in SRAMs from a 250 nm to a 22 nm design rule," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1527–1538, Jul. 2010.

- [16] G. Gasiot, D. Giot, and P. Roche, "Multiple cell upsets as the key contribution to the total SER of 65 nm CMOS SRAMs and its dependence on well engineering," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2468–2473, Dec. 2007.

- [17] G. Gasiot, D. Giot, and P. Roche, "Alpha-induced multiple cell upsets in standard and radiation hardened SRAMs manufactured in a 65 nm CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3479–3486, Dec. 2006.

- [18] J. Baggio, D. Lambert, V. Ferlet-Cavrois, P. Paillet, C. Marcandella, and O. Duhamel, "Single event upsets induced by 1–10 MeV neutrons in static-RAMs using mono-energetic neutron sources," *IEEE Trans. Nucl.* Sci., vol. 54, no. 6, pp. 2149–2155, Dec. 2007.

- [19] T. Uemura, T. Kato, H. Matsuyama, and M. Hashimoto, "Soft-error in SRAM at ultra-low voltage and impact of secondary proton in terrestrial environment," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4232–4237, Dec. 2013.

- [20] S. Hirokawa, R. Harada, M. Hashimoto, and T. Onoye, "Characterizing alpha- and neutron-induced SEU and MCU on SOTB and bulk 0.4-V SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 2, pp. 420–427, Apr. 2015.

- [21] T. Uemura, B. Chung, S. Chung, S. Lee, Y. Hwang, and S. Pae, "Impact of design and process on alpha-induced SER in 4 nm bulk-FinFET SRAM," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2023, pp. 874–881.

- [22] T. Kato, M. Hashimoto, and H. Matsuyama, "Angular sensitivity of neutron-induced single-event upsets in 12-nm FinFET SRAMs with comparison to 20-nm planar SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 7, pp. 1485–1493, Jul. 2020.

- [23] T. Sato et al., "Features of particle and heavy ion transport code system (PHITS) version 3.02," J. Nucl. Sci. Technol., vol. 55, no. 6, pp. 684–690, Jun. 2018.

- [24] K. M. Warren et al., "Application of RADSAFE to model the single event upset response of a 0.25 μm CMOS SRAM," *IEEE Trans. Nucl.* Sci., vol. 54, no. 4, pp. 898–903, Aug. 2007.

- [25] S.-I. Abe and T. Sato, "Soft error rate analysis based on multiple sensitive volume model using PHITS," J. Nucl. Sci. Technol., vol. 53, no. 3, pp. 451–458, Mar. 2016.

- [26] K. Takeuchi et al., "Characteristic charge collection mechanism observed in FinFET SRAM cells," *IEEE Trans. Nucl. Sci.*, vol. 69, no. 8, pp. 1833–1839, Aug. 2022.

- [27] S. Abe et al., "Neutron-induced soft error analysis in MOSFETs from a 65 nm to a 25 nm design rule using multi-scale Monte Carlo simulation method," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2012, pp. 894–899.

- [28] S. Manabe, Y. Watanabe, W. Liao, M. Hashimoto, and S.-I. Abe, "Estimation of muon-induced SEU rates for 65-nm bulk and UTBB-SOI SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 66, no. 7, pp. 1398–1403, Jul. 2019.

- [29] D. F. Measday, "The nuclear physics of muon capture," Phys. Rep., vol. 354, nos. 4–5, pp. 243–409, Nov. 2001.

- [30] M. Hashimoto, W. Liao, and S. Hirokawa, "Soft error rate estimation with TCAD and machine learning," in *Proc. Int. Conf. Simul. Semiconductor Processes Devices (SISPAD)*, Sep. 2017, pp. 129–132.

- [31] S. Hirokawa, R. Harada, K. Sakuta, Y. Watanabe, and M. Hashimoto, "Multiple sensitive volume based soft error rate estimation with machine learning," in *Proc. Eur. Conf. Radiat. Effects Compon. Syst. (RADECS)*, Sep. 2016, pp. 387–390.