# **PVT-induced timing error** detection through replica circuits and time redundancy in reconfigurable devices

# Dawood Alnajjar<sup>1,3a)</sup>, Yukio Mitsuyama<sup>2,3b)</sup>, Masanori Hashimoto<sup>1,3c)</sup>, and Takao Onoye<sup>1,3d)</sup>

<sup>1</sup> Department of Information Systems Engineering, Osaka University, Suita-shi, Osaka 565–0871, Japan

<sup>2</sup> School of Systems Engineering, Kochi University of Technology, Kami-shi, Kochi 782–8502, Japan

<sup>3</sup> JST, CREST, Tokyo 102–0075, Japan

a) dawood.alnajjar@ist.osaka-u.ac.jp,

b) mitsuyama.yukio@kochi-tech.ac.jp,

c) hasimoto@ist.osaka-u.ac.jp,

d) onoye@ist.osaka-u.ac.jp

LETTER

**Abstract:** This paper studies performance and timing failure probability of time-shifted redundant circuits and path-/circuit-replica circuits. Measurement-based experiments using a fabricated test chip are performed. For an approximately similar false positive error probability for the path-replica and circuit-replica, the false negative error probability of the circuit-replica is approximately two orders of magnitude less than that of the path-replica circuits. When attaining a false negative error of zero, the probability of error detection and reexecution in time-shifted redundant circuits is comparable to, or rather smaller than that of the path-replica circuits.

**Keywords:** dynamic voltage variations, voltage scaling, replica circuits, time diversity, timing errors, error prediction, error detection, variation tolerant circuits

**Classification:** Integrated circuits

#### References

- T. Kuroda, et al., "Variable supply-voltage scheme for low-power highspeed CMOS digital design," *IEEE J. Solid-State Circuits*, vol. 33, no. 3, pp. 454–462, March 1998.

- [2] J. W. Tschanz, et al., "Adaptive body bias for reducing impacts of die-todie and within-die parameter variations on microprocessor frequency and leakage," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1396–1402, Nov. 2002.

- [3] J. T. Kao, et al., "A 175-mV multiply-accumulate unit using an adaptive supply voltage and body bias architecture," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1545–1554, Nov. 2002.

- [4] J. Tschanz, et al., "Tunable replica circuits and adaptive voltagefrequency techniques for dynamic voltage, temperature, and aging variation tolerance," *Symposium on VLSI Circuits Digest of Technical Papers*, 2009.

- [5] S. Das, et al., "A self-tuning DVS processor using delay-error detection and correction," *IEEE J. Solid-State Circuits*, vol. 41, no. 4, pp. 792–804, April 2006.

- [6] S. Das, et al., "Razor II: In situ error detection and correction for PVT and SER tolerance," *IEEE J. Solid-State Circuits*, vol. 44, no. 1, pp. 32– 48, Jan. 2009.

- [7] H. Fuketa, et al., "Adaptive performance compensation with in-situ timing error predictive sensors for subthreshold circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 2, pp. 333–343, Feb. 2012.

- [8] N. Kanekawa, et al., Dependability in electronic systems, Springer, 2011.

- [9] J. Freijedo, et al., "Impact of power supply voltage variations on FPGAbased digital systems performance," J. Low Power Electron., vol. 6, pp. 339–349, Aug. 2010.

- [10] A. Kumar, et al., "FPGA design for timing yield under process variations," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 18, no. 3, pp. 423–435, March 2010.

- [11] H. Yu, et al., "Fine-grained characterization of process variation in FP-GAs," Proc. Int. Conf. Field Programmable Technology, pp. 138–145, Dec. 2010.

- [12] D. Alnajjar, et al., "Coarse-grained dynamically reconfigurable architecture with flexible reliability," *Proc. Field Programmable Logic and Applications*, pp. 186–192, Sept. 2009.

#### **1** Introduction

With the aggressive process scaling, performance variation due to manufacturing variability has become a serious concern preventing chip designers from pursuing high performance with a high timing yield. This variation is classified as static variation since it is determined in the manufacturing process and is constant after the fabrication. On the other hand, the effect of transistor aging and dynamic variation in supply voltage and temperature is also becoming more prominent. For avoiding timing failures due to both static and dynamic variations, design margins are being built into the operating voltage and frequency settings in order to account for the worst case conditions. However, imposing such guard-bands prohibits the user from exploiting the high performance offered by increasing the operation frequency, or the low power consumption offered by reducing the supply voltage.

Traditionally, replica circuits have been used for performance monitoring. Adaptive control techniques with a critical path replica have been presented in [1, 2, 3]. Recently, [4] applied Tunable Replica Circuits (TRC) to a microprocessor and the performance improvement and power reduction are demonstrated using a 45 nm test chip. The path-replica circuits in the

presented techniques, which mimics the critical path, is fully exercised every cycle. This suggests that these techniques aim to sustain a necessary and sufficient timing margin at all times in all the paths. On the other hand, the critical paths are not activated often in most circuits. This means that in most cycles, the timing margins of the activated paths are larger than necessary.

Such a stochastic property on critical path activation is exploited for aggressive power reduction in [4, 5, 6, 7]. [7] predicts timing error occurrences using timing error predictive flip-flops, and proactive performance adaptation is executed. On the other hand, [4, 5, 6] detect timing errors using Error Detection Sequentials (EDS), which are also known as Razor flip-flops. Upon detecting a timing error in the critical path, re-execution and recovery occur. EDS is a flip-flop accompanied by an extra latch that also captures the data slightly after the system clock. The outputs of the main flip-flop and the latch are compared to check whether a timing error occurs or not. As the output data arrives later than the system clock edge, the outputs become different, and the EDS detects a timing error.

Recently, timing error prediction using TRC is utilized not only for coping with static manufacturing variability but also for overcoming dynamic variations [4]. For example, the TRC circuit could be designed so that it fails when a dynamic voltage droop occurs inducing a timing error. The TRC consisting of different logic gates such as inverters, NAND, and other elements needs to mimic the critical paths. Although the longest critical path varies depending on manufacturing variability, the delay of TRC must be larger than that of the longest path in all the variational device parameter space. Furthermore, for handling dynamic voltage variations, the sensitivity of the TRC to supply voltage should be the same as that of the real circuit. Due to such a difficulty, it is used only for high-end processors. Heavy tuning is required to calibrate the sensitivity of the TRC to track critical path delays of the real circuit. As TRC represents a replica of the critical path, it will be referred to as path-replica throughout this paper.

When it comes to reconfigurable devices, implementing path-replicas has a higher compatibility since the behavior of the real circuit can be exactly mimicked by simply mapping the path-replica again on the available resources, and heavy tuning of the path-replica circuit is no longer necessary since the exact circuit is replicated. In addition, in case of coarse-grained reconfigurable device, the number of critical path candidates is quite limited, and just a simple tuning to pad a small delay is sufficient. Thus, the mismatch problem between the path-replica and the real circuit is less significant. On the other hand, as mentioned above, the critical paths are not often activated, and hence most of the timing error predictions by the path-replica circuit are false positive. This false positive prediction could significantly degrade the application throughput due to the frequent recovery through re-execution.

Taking advantage of the stochastic property of critical path activation, a complete replica of the circuit can be implemented in parallel. The critical path in the replica circuit will be activated only when the critical path in the

real circuit is activated. This means that extra margins imposed by activating the critical path every cycle are no longer necessary, and full performance and less power consumption can be achieved as it trades-off area with performance/power reducing the false positive prediction while keeping the false negative low. This circuit will be referred to as circuit-replica throughout this paper. Moreover, inserting EDS [4, 5, 6], mentioned previously, is an area-efficient implementation of the circuit-replica; however, in order to use it in reconfigurable devices, EDS must be built-in.

Introducing a time-redundant circuit is one of concurrent error detection techniques, and it is often adopted in reliability-demanding applications [8]. The same computation is executed after a certain period of time, and the results are compared. The advantage of time redundancy is that the time diversity of the operating condition reducing the chance of observing an identical timing error in the main and redundant circuit. In addition, the stochastic property on critical path activation mentioned above can be exploited, thereby significantly reducing the false positive prediction when compared to the path-replica circuit. Time-shifted redundant circuits are also compatible with reconfigurable devices where they can be implemented easily.

Nevertheless, in the field of reconfigurable devices such as Field Programmable Gate Arrays (FPGAs), sub-optimal approaches such as imposing guard-bands are still utilized to accommodate the Process, power supply Voltage, and Temperature (PVT) variations, and the maximum allowable clock frequencies reported by vendor synthesis, placement and routing tools are significantly lower than the ones that the device can really deliver [9]. Although there is ongoing research on the performance reliability and improvement of reconfigurable devices [10, 11], none demonstrate the value and effectiveness of path-replica circuit for PVT. This is the first work that introduces pathreplica circuits in reconfigurable devices addressing PVT variations as far as the authors have investigated.

Motivated by the compatibility of time-shifted redundant circuits and path-replica circuits with reconfigurable devices, this work introduces pathreplica circuits in reconfigurable devices, and evaluates the effectiveness of using time-shifted redundant circuits and path/circuit-replica circuits in detecting and predicting timing error occurrences in a real circuit mapped on a reconfigurable device. An application is implemented on a coarse-grained reconfigurable architecture developed in one of our previous works [12], and measurement-based experiments using a fabricated test chip are performed. Comparison results show how much power reduction and throughput improvement can be obtained by exploiting low probability of critical path activation on the expense of silicon area, and the trade-offs offered by each approach in terms of performance, power dissipation, and error probability are presented. The immunity to dynamic voltage variation is compared, and the utility of time redundancy is presented.

#### 2 Replica circuit and time redundancy

#### 2.1 Replica circuits

The path-replica circuit is designed such that its own delay is larger than that of the longest path in the real circuit. It is noteworthy that this relation should hold even under static manufacturing variability and dynamic voltage variation, taking into account the fact that the longest path varies according to these variations. A performance adaptation technique such as supply voltage scaling is then applied, and the supply voltage is reduced to the voltage at which the path-replica circuit is at the edge of causing timing errors. Here, if the delay of the path-replica circuit is much larger than the longest path delay in the real circuit, the delay of the real circuit is overestimated resulting in unnecessary performance loss. On the other hand, if the delay of path-replica circuit is smaller than the longest path delay in a certain operating condition, timing errors in the real circuit will occur. Thus, depending on the path-replica circuit design, the achievable circuit performance and timing failure probability vary. On the other hand, the circuit-replica takes advantage of the stochastic property of critical path activation, and the critical path is activated only when that in the real circuit is activated.

The path-replica circuit can be also used for dynamic variation tolerance by exercising it every cycle [4]. When the path-replica causes a timing error, there is a possibility that timing errors happened in the real circuit. Once a timing error happens in the path-replica, the states of the real circuit are recovered and the computation is re-executed. It is likely that the operating condition of the second computation is different from that of the first one, and the second computation might succeed. Another option for ensuring the success of the re-execution could be adopting a multi-cycle operation for the problematic cycles. On the other hand, the critical paths in the real circuit are not activated so often, while the path-replica is excited every cycle. This means that even when timing errors occur in the path-replica, timing errors do not necessarily occur in the real circuit. When the sensitivity of the path-replica to the supply voltage droop is different from that of the critical paths in the real circuit, there is a possibility that the path-replica does not cause a timing error even when the real circuit causes a timing error. On the other hand, if the delay of path-replica is much larger than that of the real circuit, timing errors in the path-replica might appear more frequently. The timing errors that occur solely in the path-replica involve unnecessary recovery and re-execution, and hence they degrade application performance and throughput. Thus, depending on the path-replica circuit design, the application performance and timing failure probability under dynamic variation also vary.

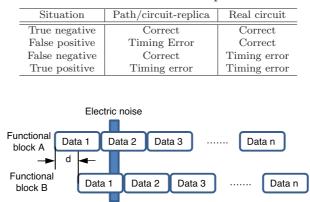

In discussing the error detection for path/circuit-replica circuits, we need to consider four situations, as listed in Table I. The first situation (true negative) is that where both the replica and the real circuits work without timing errors, which corresponds to the normal operation. In the second situation (false positive), the replica circuit produces a timing error, while

| Table I. For | ur situations | of replica | circuits. |

|--------------|---------------|------------|-----------|

|--------------|---------------|------------|-----------|

Fig. 1. Time diversity of redundant computation.

the real circuit does not. In this case, recovery is performed, decreasing the throughput depending on the number of the cycles necessary for the recovery phase. On the other hand, a false negative situation arises when the replica circuit does not produce a timing error while the real circuit does. The false negative error is not desirable for reliable applications, and a value converging to zero would be most appealing. In case of path-replica, in order to reduce the false negative errors, the delay of the path-replica must be increased, failing more frequently. However, it increases the probability of the false positive, and sacrifices the application throughput and circuit speed.

#### 2.2 Time redundancy

Concurrent error checking is a popular approach for fault tolerance, and time redundancy is one of the concurrent error checking techniques. For dynamic voltage variation tolerance, the concept of time diversity is effective. The same error outbreak can be prevented by diversifying the time of operation of redundant computation. Figure 1 illustrates the time diversity and its effect. The functionalities of functional blocks A and B are identical, the input data is temporally shifted, and the outputs for the same input data are compared in order to check for errors. In this illustration, the two functional blocks are processing different data at the time the electrical noise occurs, and the outputs of these two blocks are affected in different ways. If inconsistency is found in the outputs, we notice that there was an error occurrence, and accordingly we perform recovery and re-execution. An important factor of time redundancy is the amount of shifting time  $\mathbf{d}$ , which characterizes the immunity to the dynamic variation. As d becomes larger, temporally-long variations can be tolerated, however, the additional hardware necessary for time shifting increases. In contrast, when  $\mathbf{d}$  is small, for example just a single clock cycle, the noise spreading in successive two cycles might not be tolerated; i.e. the same timing error might occur in both circuits causing identical incorrect output.

In case of time redundancy, we have three situations, as listed in Table II. When the outputs of the two blocks are identical, there are two situations;

Table II. Three situations of time redundancy.

|                | Outputs   | Real circuit |

|----------------|-----------|--------------|

| True negative  | Identical | Correct      |

| False negative | Identical | Timing error |

| True positive  | Different | Timing error |

|                |           |              |

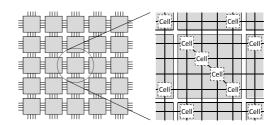

Fig. 2. Reconfigurable architecture overview.

true negative and false negative. This false negative occurs when both blocks cause the same timing error. In case of time redundancy, both blocks are equally treated, and hence the inconsistency of the outputs is regarded as the timing error in the real circuit. Therefore, false positive is not included in the table. Thus, to reduce the probability of false negative, we need to intensify time diversity and decrease the probability that both the circuits experience the same timing error.

#### **3** Reconfigurable architecture overview

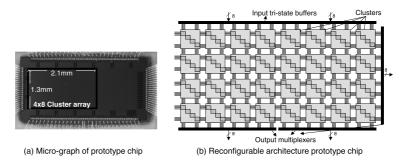

Figure 2 illustrates the overview of the reconfigurable architecture used in this study [12]. Clusters, which are basic elements of this architecture, are placed repeatedly in a two-dimensional array. Each cluster contains four cells connected to each other using diagonal tracks or connected to the cells in the adjacent cluster using horizontal and vertical tracks. The architecture also posses some embedded flexible reliability mechanism, but they will not be explained as they are out of the scope of this paper. Each cell can perform addition and subtraction operations with or without cooperation of the neighboring cells in the same cluster. It also can be configured to perform logical operations such as logical AND and OR, multiplexing, and fixed or variable shifting. A  $4 \times 8$  cluster array was fabricated in a 65 nm CMOS process. The micro-graph is depicted in Fig. 3 (a), and the design is shown

Fig. 3. Reconfigurable architecture prototype chip and micrograph.

© IEICE 2013 DOI: 10.1587/elex.10.20130081 Received January 31, 2013 Accepted February 08, 2013 Published March 14, 2013

in Fig. 3 (b). This prototype chip will be used throughout the study in this work.

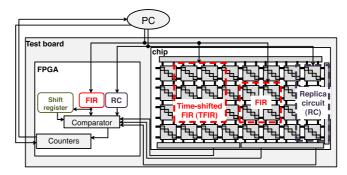

# 4 Experimental setup

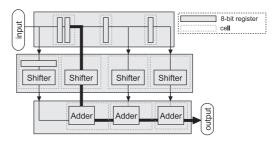

The setup of the experiment is shown in Fig. 4. It consists of a PC, a test board containing a Stratix II FPGA connected to the prototype chip of the reconfigurable architecture. The application chosen to be mapped on the reconfigurable architecture is a 4-tap FIR filter. One of the possible implementations is shown in Fig. 5. The constants of the mapped FIR filter were all identical and equal to 0.25, which was represented by a 2-bit shift to the right. On the prototype chip, an FIR filter, a time-shifted FIR filter (TFIR), and the path-replica circuit (RC) were mapped. Similarly, on the FPGA an FIR, RC, a shift register, and a comparator circuit were implemented. The circuits on the FPGA are responsible for generating the correct outputs for comparison purposes. Note that both the FPGA and the prototype chips are necessary since timing errors would arise in the prototype chip as it undergoes dynamic and static supply voltage variation, and the FPGA is used for detecting such errors.

Fig. 4. Setup of the experiment.

Fig. 5. 4-tap FIR filter.

In order to implement the path-replica circuit, the critical path of the FIR filter was identified and is highlighted with the thick line showing the flow of data on it in Fig. 5. It is noteworthy that the delay of the path-replica circuit should be equal or larger than that of the critical path of the real circuit in order to make sure that path-replica fails to produce output when the real circuit does. Knowing this, three different path-replica circuits were prepared with different delays added to the critical path length of the real application: 148 ps, 308 ps, and 468 ps. The delays were generated by using

the routing resources on the chip. They were estimated from design data, not from measurement results. When the delay is larger than 468 ps, the pathreplica always fails at nominal voltage without any dynamic noise. As for the time-shifted FIR filter, the key implementation parameter is the amount of cycles by which the FIR is shifted, and it characterizes the diversity of dynamic operating condition, as mentioned in Section 2.2. In this study, 1-, 2-, 4- and 8-cycle time shifting are considered.

The PC generates random inputs for the FIR circuits. We also need to give an input pattern to RC. This input to the RC has to be carefully selected in order to exercise the critical path every cycle. The comparator circuit compares the outputs of the chip with the generated outputs of the RCs and the FIRs. It should be noted that the main purpose of the RC on the FPGA is to just produce the expected output in order to compare with the output of RC circuit on the prototype chip. In this study, two types of experiments are performed and are as follows in the next sections.

## 4.1 Static variation experiments

In the static variation experiments, the supply voltage is set to different values between 1.0 V to 1.2 V, and the output of the RC and FIR are monitored and compared. This range of supply voltage includes voltage over-scaling accompanied with timing-violating paths. For each supply voltage value, the comparisons are performed for 2 minutes, allowing approximately  $1.6 \times 10^9$  comparisons at a 26 MHz operating frequency. In these experiments, there is no significance in changing the delay of the time-shifted FIR, therefore, it will be fixed to 1 cycle delay. It will be regarded as a circuit-replica, and not a time-shifted circuit. It will be referred to as FIR replica circuit (FIR RC) in static variation experiments. This FIR RC is very important as it serves as a replica for the FIR without extra delay on the critical path, and it also takes advantage of the stochastic probability of the critical path activation, unlike the RC circuits.

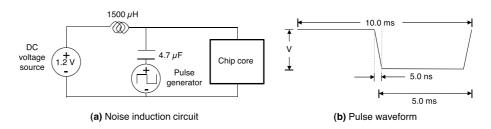

## 4.2 Dynamic variation experiments

In the dynamic variation experiments, dynamic noises are periodically injected to a 1.2 V supply voltage through a capacitor by a pulse generator, as shown in Fig. 6 (a). The waveform at the output of the pulse generator is shown in Fig. 6 (b). The dynamic noise appears at the rising and falling edges. The amplitude at the pins of the chip package can be manipulated by

Fig. 6. Noise injection circuit and pulse waveform.

© IEICE 2013 DOI: 10.1587/elex.10.20130081 Received January 31, 2013 Accepted February 08, 2013 Published March 14, 2013

varying V in Fig. 6 (b). V was set to 1 V, 2 V, and 3 V causing a variation of  $\Delta 130 \text{ mV}$ ,  $\Delta 210 \text{ mV}$ , and  $\Delta 270 \text{ mV}$ , respectively at the pins of the chip package. Approximately  $16 \times 10^9$  comparisons were executed in a period of 20 minutes each. In dynamic variation experiments, time-shifted FIR will be referred to as TFIR-1, TFIR-2, TFIR-4, and TFIR-8 and it will be regarded as a time-redundant circuit.

# 5 Results and discussion

## 5.1 Static variation

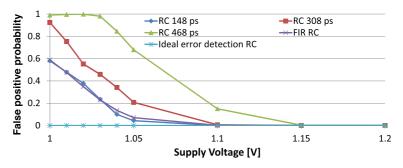

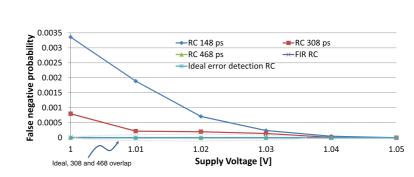

The results of static variation experiment for the replica circuits are shown in Fig. 7 and Fig. 8. The notation of RC 148 ps denotes the results of the RC with 148 ps additional delay. The ideal error detection RC is a virtual circuit that ideally produces timing errors only when there are timing errors in the real circuit, which means false negative and false positive are zero. It is demonstrated as the reference of the upper bound performance.

Figures 7 and 8 demonstrate the importance of selecting the appropriate path-replica circuit for the designated application. Choosing an RC circuit with larger delay will increase the number of false positive errors while minimizing the number of false negative ones in the real circuit. It involves the increase in the number of recovery cycles, and thereby reduces the throughput. Looking at Fig. 7, we see that the FIR RC and the RC 148 ps offer approximately the same false positive probability. However, by looking at Fig. 8, we see that the false negative error probability of RC 148 ps is  $3.336 \times 10^{-3}$  and

Fig. 7. False positive probability obtained from static variation experiment of RC.

Fig. 8. False negative probability obtained from static variation experiments of RC. Note that the ideal, the RC 308 ps, and the RC 468 ps overlap.

that of FIR RC is  $1 \times 10^{-5}$  at 1 V. That is approximately two orders of magnitude more when compared to FIR RC. This means that FIR RC reduces false positive errors while keeping the false negative error count low. Remind that the main advantage of FIR RC from RC is the active use of stochastic property of the critical path activation, and this two orders of magnitude difference comes from the utilization of this property.

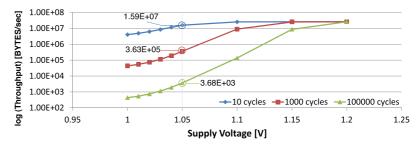

For understanding the significance of the false negative probability shown in Fig. 8, we study the effect of this probability on the overall throughput of the circuit. In Fig. 9, we assuming that the number of recovery cycles for each RC failure is 10, 1k, and 100k cycles. We show the overall throughput versus the supply voltage for the FIR RC. For a supply voltage of 1.05 V, the throughputs for recovery phases of 10 cycles, 1k cycles, and 100k cycles are equal to  $1.59 \times 10^7$ ,  $3.63 \times 10^5$ , and  $3.68 \times 10^3$  which have a difference of approximately two orders of magnitude from one to the next.

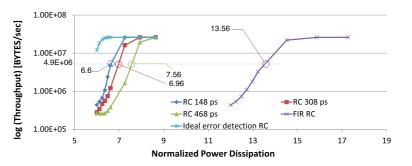

We next demonstrate the trade-off between the throughput and power. Assuming that the number of recovery cycles for each predicted error is 100, and that the re-execution will be correct, then throughput versus the normalized dissipated power is shown in Fig. 10. The normalized power dissipation is calculated as a first order analysis assuming it is proportional to supply voltage squared multiplied by the number of cells used. Note that the cells used only for padding delay are not included in the cell count since the power consumption is minor and negligible.

It can be observed that there is a considerable trade-off between the normalized power and throughput for each circuit. In addition, the curves

**Fig. 9.** Example demonstrating the effect of false negative probability on throughput.

Fig. 10. Example demonstrating throughput vs. normalized dissipated power for each circuit.

are different depending on the error detection circuits, as we expected. If a throughput of  $4.9 \times 10^6$  is required, then the minimum normalized dissipated power for the RC 148 ps, RC 308 ps, RC 468 ps, and FIR RC is 6.6, 6.96, 7.56, and 13.56, respectively.

# 5.2 Dynamic variation

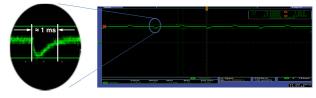

In the experiments of dynamic variation, setting the V to 1 V and 2 V did not induce any timing errors. However, results for setting V to 3 V causing a variation of  $\Delta 270 \,\mathrm{mV}$  in the supply voltage produced several significant results. The  $\Delta 270 \,\mathrm{mV}$  noise signal taken by the oscilloscope is shown in Fig. 11. The results are summarized in Table III. TFIR circuits offer zero false negative errors, which is highly desirable for reliability-demanding applications, though RC 148 ps and 308 ps circuits produce false negative. RC 468 ps circuit attains zero false negative, but the probability of error detection and re-execution is higher. The important point here is that TFIR attains zero false negative while the probability of re-execution is comparable, or rather lower than that of the RC circuits.

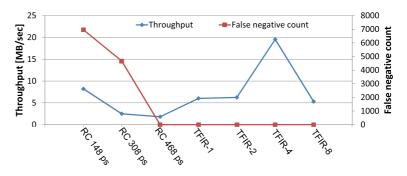

Figure 12 shows the throughput and the false negative count for each

Fig. 11. Noise signal induced from a pulse of 3 V in amplitude.

| Table III. | False negative error, false positive, true positive, |  |  |  |

|------------|------------------------------------------------------|--|--|--|

|            | and re-execution probabilities.                      |  |  |  |

|                                 | Path-replica circuits    |                          |                      | Time-redundant circuits  |                          |                          |                          |

|---------------------------------|--------------------------|--------------------------|----------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| Probability                     | RC 148  ps               | $\rm RC~308ps$           | $\rm RC~468ps$       | TFIR-1                   | TFIR-2                   | TFIR-4                   | TFIR-8                   |

| False positive                  |                          |                          |                      | -                        | -                        | -                        | -                        |

| False negative                  | $4.3 \mathrm{x} 10^{-7}$ | $2.9 \mathrm{x} 10^{-7}$ | 0                    | 0                        | 0                        | 0                        | 0                        |

| True positive                   | $5.0 \times 10^{-8}$     | $3.4 \mathrm{x} 10^{-7}$ | $9.0 \times 10^{-8}$ | $3.3 x 10^{-3}$          | $3.2 \times 10^{-3}$     | $3.3 \mathrm{x} 10^{-4}$ | $3.9 \mathrm{x} 10^{-3}$ |

| $\operatorname{Re-execution}^*$ | $2.2 \text{x} 10^{-3}$   | $9.4 \mathrm{x} 10^{-3}$ | $1.3 x 10^{-2}$      | $3.3 \mathrm{x} 10^{-3}$ | $3.2 \mathrm{x} 10^{-3}$ | $3.3 \mathrm{x} 10^{-4}$ | $3.9 \mathrm{x} 10^{-3}$ |

\* Re-execution prob. is the summation of true positive and false positive probabilities

Fig. 12. Throughput and false negative count collected in the dynamic noise experiments.

scheme. The RC 148 ps shows the highest false negative error count. Focusing on the near zero false negative error count, we can see that the TFIR circuits offer a higher throughput when compared to the RC 468 ps.

In Fig. 12, the TFIR improves the throughput up to 4-cycle shifting (TFIR-4), which can be explained by the time diversity as explained in Section 2.2. On the other hand, in case of 8-cycle shifting (TFIR-8), the throughput becomes comparable to that of TFIR-2. In this experiment, we solely observed the noise waveform outside the chip as shown in Fig. 11, and the noise that is actually given to the FIR filter inside the chip cannot be assessed. This non-monotonicity in throughput might be related to the resonance frequency on the chip, and 8-cycle shifting is affected by the resonance. Further study is necessary, but TFIR-4 should be selected for tolerating dynamic voltage variation in this test case.

# 6 Conclusion

A study on performance and time failure probability of utilizing time-shifted redundant circuits and replica circuits has been demonstrated. Measurementbased experiments using a fabricated test chip are performed. It is shown that the time-shifted redundant circuit and circuit-replicas reduces false positive errors while keeping the false negative error count low. When having an approximately similar false positive error probability, false negative error probability of the circuit-replica is approximately two orders of magnitude less than that of the path-replica circuits. For zero false negative, the probability of re-execution after error detection is higher in path-replica circuits than in time-shifted circuits.

# Acknowledgment

The VLSI chip in this study has been fabricated in the chip fabrication program of VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with eShuttle Inc. and Fujitsu Semiconductor Ltd. This study is partially supported by NEDO.